计组实验报告

实验一 存储器实验

一、实验目的

1、掌握FPGA中lpm_ROM只读存储器配置方法。

2、用文本编辑器编辑mif文件配置ROM,加载于ROM中;

3、验证FPGA中mega_lpm_ROM的功能。

二.实验原理

ALTERA的FPGA中有许多可调用的LPM (Library Parameterized Modules)参数化的模块库,可构成如lpm_rom、lpm_ram_io、lpm_fifo、lpm_ram_dq的存储器结构。CPU中的重要部件,如RAM、ROM可直接调用他们构成,因此在FPGA中利用嵌入式阵列块EAB可以构成各种结构的存储器,lpm_ROM是其中的一种。lpm_ROM有3组信号:地址信号address[ ]、数据信号q[ ]、时钟信号clk。由于ROM是只读存储器,所以它的数据口是单向的输出端口,ROM中的数据是在对FPGA现场配置时,通过配置文件一起写入存储单元的。

三.实验步骤

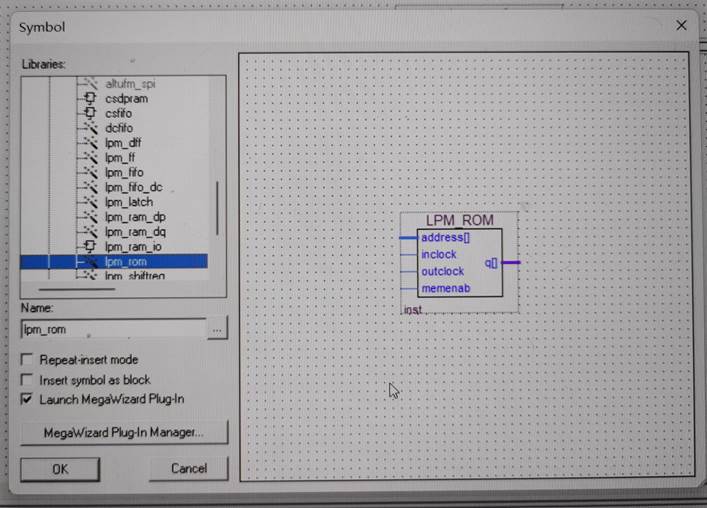

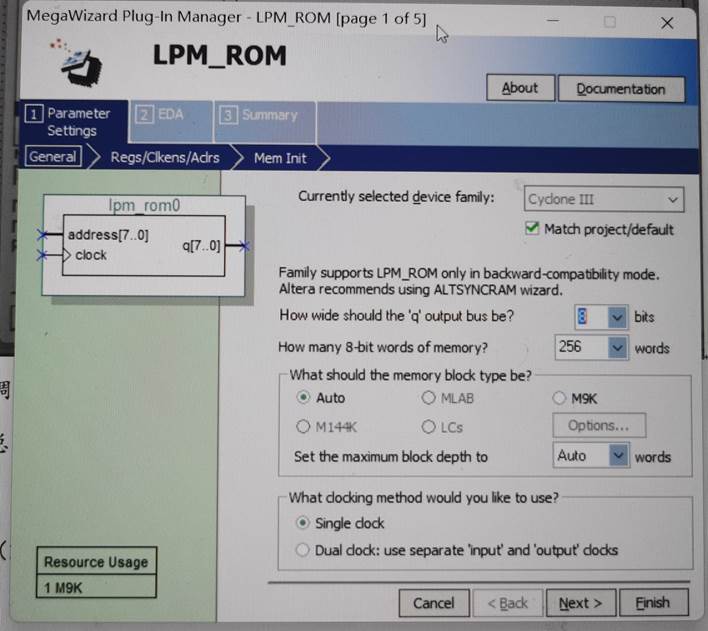

(1)用图形编辑,进入mega_lpm元件库,元件库

调用lpm_rom元件,设置时钟信号clk,地址总线宽度a[7..0],数据总线宽度q[7..0],即地址8位,数据8位,并添加输入输出引脚。注意需要在配置的最后一步添加.hex或.mif文件,作为ROM元件的存储数据。

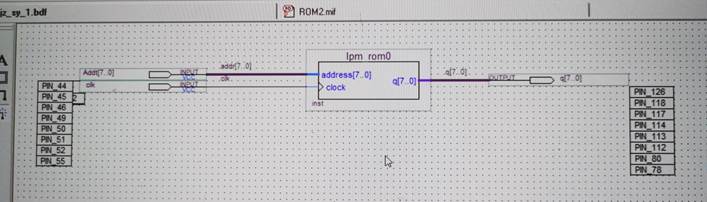

根据实验要求所设计的存储器电路图如图所示,其中输入为一根时钟信号,一个由八根地址线组成的地址总线。输入为由八根数据线组成的数据总线。

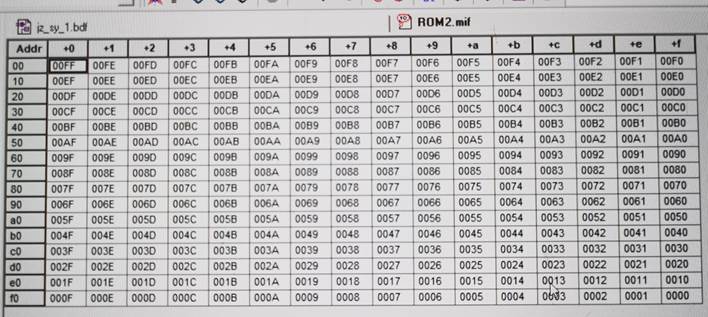

所使用的MIF数据如图所示,满足所选择的数据位置与其中的数据内容算数求和得到的结果为FF,方便验收。设置每一行的cell的值为16,与16进制的个位对应,每一列的数据与16进制的十位对应

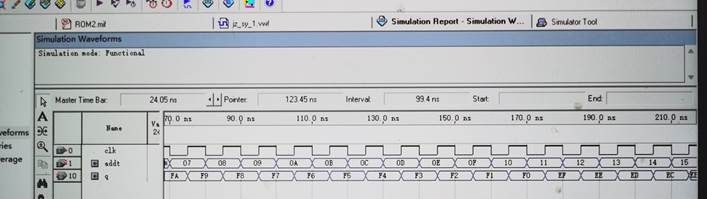

(2)波形仿真

打开QuartusII,选File -> New other files -> Vector Waveform File,点击OK进入仿真界面。

点Node Finder,点list 选中需要仿真的信号,:a[5..0],clk ,[7..0]点击 OK -> OK.加入信号,点快捷键仿真。

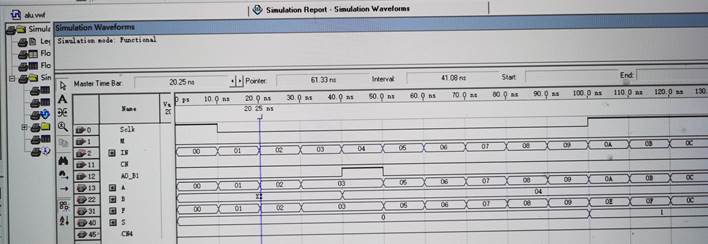

得到的波形仿真如图所示,其中将输入clk输入为矩形信号,在0与1之间等时间间隔变动。地址信号设为数值,由00递增至FF。由于LPM_ROM存储器的时钟信号为上升沿有效,故在上升沿时将地址读入,并输出保存在MIF文件内对应地址上的数据,并且在下一个上升沿到来时将读取出的数据输出。

比如在某一个上升沿时,读入ADDR的值为0B,根据MIF文件的记录数据,0B地址下的数据为F4,与输出的F4相对应,验证了LPM_ROM的功能。

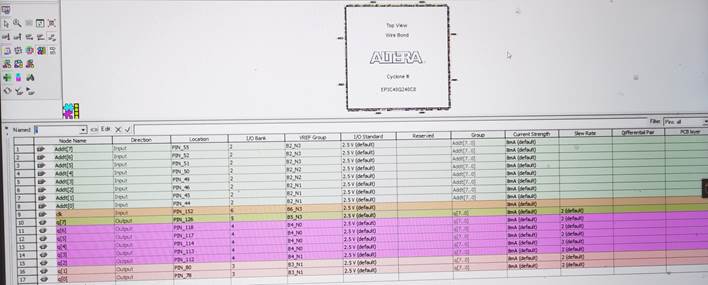

(3)引脚锁定

选择菜单Assignments->pins->Location,根据实验电路结构图NO.0和芯片引脚对照表, 查出a[5..0],clk ,[7..0] 在核心芯片EP3C40Q240C8上所对应的引脚号:

a[5]——-PIO 13——-51

a[4]——-PIO 12——-50

a[3]——-PIO 11——-49

a[2]——-PIO 10——46

a[1]——-PIO 9——–45

a[0]——-PIO 8——–44

clk——–CLOCK0—152

q[7]——-PIO 31—–126

q[6]——-PIO 30—–118

q[5]——-PIO 29—–117

q[4]——-PIO 28——114

q[3]——-PIO 27——113

q[2]——-PIO 26——112

q[1]——-PIO 25——80

q[0]——-PIO 24——78

绑定好的引脚数据如下图

(4)下载验证

将电脑与实验箱通过并口连接接好,点快捷键,在出现的lpm_rom.sof文件上, 选中program/configure点快捷键 。 即可设计下载到FPGA中。最后是用实验箱进行硬件测试。

四、实验创新

根据试验箱上的指示灯可以看出,用于标识数字的共两位,其中每位均有4盏LED指示灯进行数据显示,可表示2个16位的数据作为地址输入。教程中仅仅提供了40H的数据,还剩余B0H的数据没有被利用。故做出改变,将地址线调整至8位。并且为了方便验收,将MIF中的数据设置为满足所选择的数据位置与其中的数据内容算数求和得到的结果为FF。

五、实验心得

ROM是重要的存储器结构,经过本次实验,增加了对该元件功能上的理解。

实验二 运算器实验

一.实验目的

了解简单运算器的数据传输通路。

验证运算功能发生器的组合功能。

掌握算术逻辑运算加、减、与的工作原理。

二.实验内容

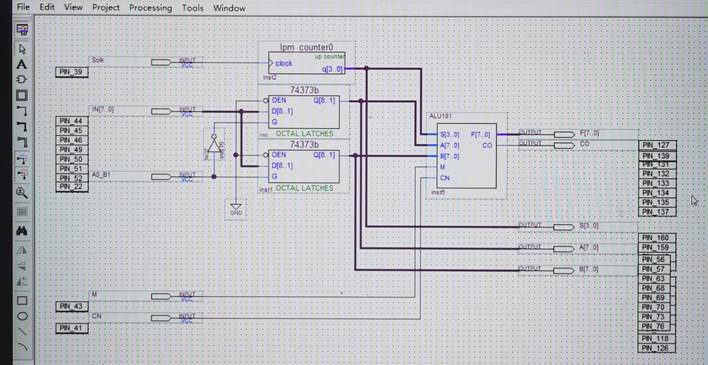

1、实验原理

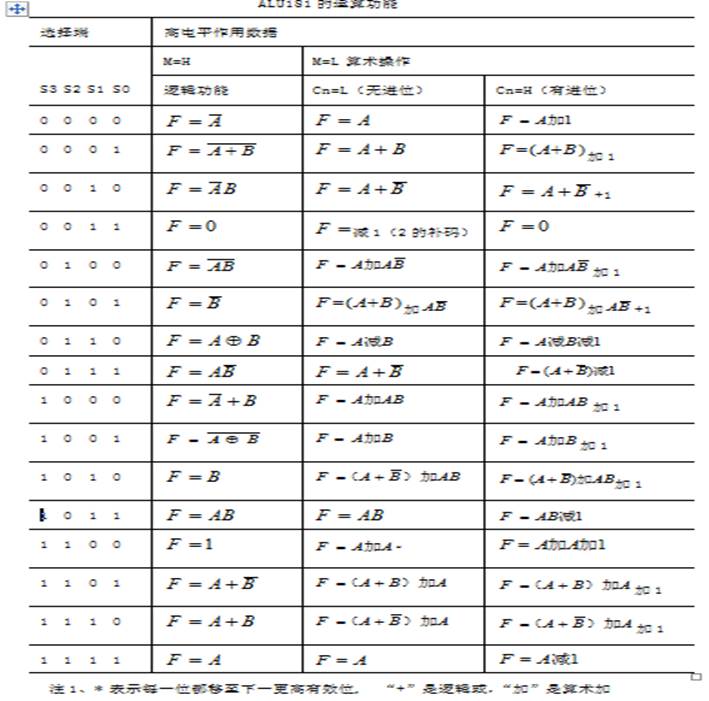

算术逻辑单元运算器ALU181根据74LS181的功能,用VHDL硬件描述语言编辑而成,构成8位字长的ALU。参加运算的两个8位数据分别为A[7..0]和B[7..0],运算模式由S[3..0]的16种组合决定,S[3..0]的值由4位2进制计数器LPM_COUNTER产生,计数时钟是Sclk(图2-1);此外,设M=0,选择算术运算,M=1为逻辑运算,CN为低位的进位位;F[7..0]为输出结果,CO为运算后的输出进位位。两个8位数据由总线IN[7..0]分别通过两个电平锁存器74373锁入,ALU功能如表所示。

2、真值表

三.实验步骤

(1)以原理图方式建立顶层文件工程

选择图形方式,电路图,从Quartus II的基本元件库中将各元件调入图形编辑窗口、连线,添加输入输出引脚。

(2)设计ALU元件

在Quartus II 环境下,编辑器Text Editor输入ALU181.VHD算术逻辑单元文件,并将文件制作成一个可调用的原理图元件。

原理图代码如下:

1 | LIBRARY IEEE; |

(3)芯片编程Programming

打开编程窗口。将配置文件ALU.sof下载到FPGA中。

(4)选择实验系统的电路模式是NO.0,验证ALU的运算器的算术运算和逻辑运算功能

根据表2-1,从键盘输入数据A[7..0]和B[7..0],并设置S[3..0]、M、Cy,验证ALU运算器的算术运算和逻辑运算功能,记录实验数据。

四、实验波形图

根据上述的波形图可以用于检验所给的元件的功能。

当S的数值为0,M的值为0即处于算术操作状态,根据所给的功能表F=A,与图示的波形图得出的结论A=F相符,故验证了所给元件得功能。

五、实验心得

经过本次实验,了解了简单运算器的数据传输通路,分析了各模块的作用,模拟了简单运算器的运行,并验证了功能。

实验三 节拍脉冲发生器时序电路实验

一、实验目的

(1)掌握节拍脉冲发生器的设计方法和工作原理。

(2)理解节拍脉冲发生器的工作原理。

二、实验原理

计算机之所以能够按照人们事先规定的顺序进行一系列的操作或运算,就是因为它的控制部分能够按一定的先后顺序正确地发出一系列相应的控制信号。这就要求计算机必须有时序电路。控制信号就是根据时序信号产生的。本实验说明时序电路中节拍脉冲发生器的工作原理。

三、连续运行电路

(1)电路图

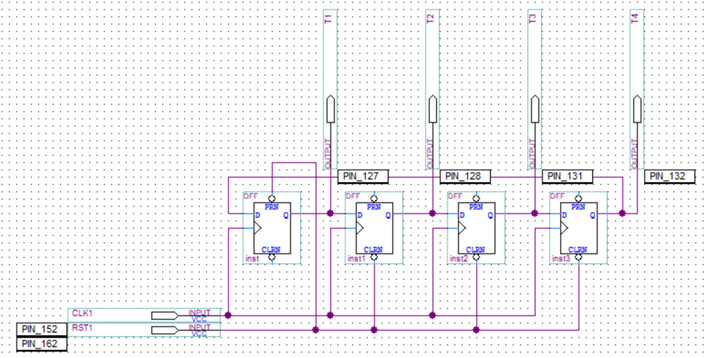

如图所示,输入CLK1发送时钟信号,连续运行电路由四块D触发器组成,接在同一个时钟信号上。输入RST1为清零端,对第一个D触发器为同步置数端清零,对后面三个D触发器为异步清零端清零

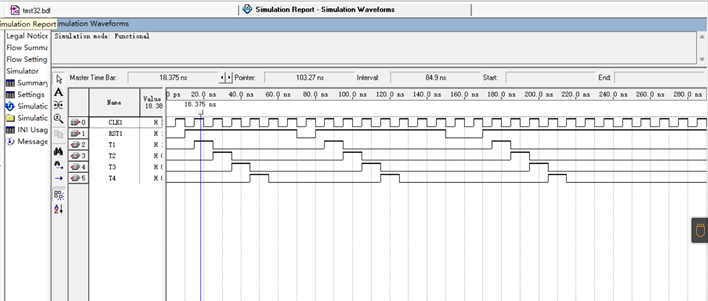

(2)波形图

波形图如图所示,脉冲信号以此向后传递,并在输出端以此输出脉冲信号,在实验箱上呈现1、2、4、8循环报数。由于清零端为低电平有效,如果清零端接收到了低电平信号,会立即清零并且持续发出数值为1的信号

四、单步运行电路

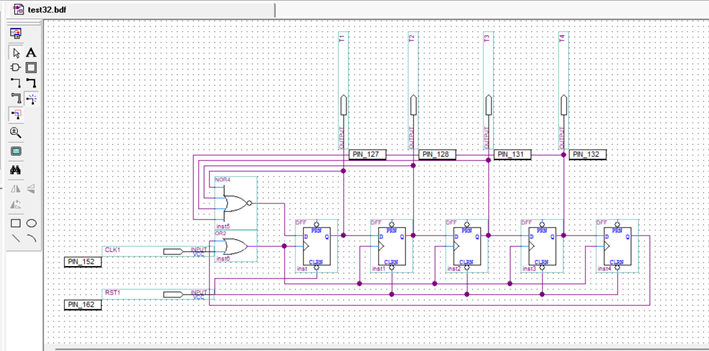

(1)电路图

如图所示为单步运行电路的电路图,该电路由五块D触发器组成。其中CLK1输出依然为时钟信号,不过与连续运行电路不同,时钟信号会与第五块D触发器的输出信号进行或运算。当输出Q5为0时时钟信号正常给到五块D触发器上。但是当输出Q5为1时,会覆盖掉时钟的周期信号,转而提供一直为1的信号,使各D触发器暂停工作。

再对各个D触发器的输出进行分析,第一至四触发器分别依次输出值为1、2、4、8的脉冲信号。输出端组成一个门电路,分别取或非运算,即当四个脉冲输出均为0时输出高电平信号,接在第一个D触发器数值位上。

与此同时,当第四个D触发器输出信号后,第五个D触发器输入端接收到高电平,并在下一个时钟信号到来时输出1信号,根据上面的分析,这个1信号会堵住时钟信号,使各个D触发器工作暂停。

这个时候由于RST1为低电平有效,当RST1给出一个低电平信号时,将各个D触发器置零,会将Q5的输出变为0,恢复时钟信号的输入,各个D触发器开始运行。

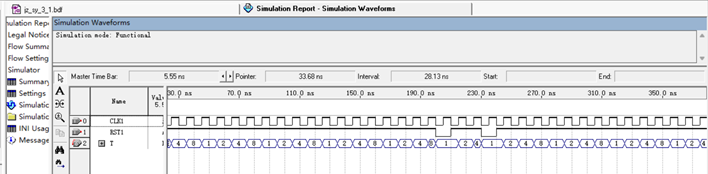

(2)波形图

根据波形图所示,当且仅当接收到低电平的RST1信号,哥哥触发器才会开始工作,依次输出值为1、2、4、8的脉冲信号。

五、实验创新点

根据上面的分析,要暂停各个触发器,需要一个高电平与时钟信号取或运算。发现输出端组成一个门电路,分别取或非运算,即当四个脉冲输出均为0时输出高电平信号,接在第一个触发器的数值位。而这个高电平信号也可以与时钟信号取或运算,即取代了第五个D触发器输出端的作用,可以实现电路的简化。

六、实验心得

理解了连续和单步脉冲电路的工作原理,并且能够根据原理图进行简化的调整。

实验四 程序计数器PC和地址寄存器AR

一、实验目的

1.掌握地址单元的工作原理。

2.掌握的两种工作方式,加1计数和重装计数器初值的实现方法;

3.掌握地址寄存器从程序计数器获得数据和从内部总线获得数据的实现方法。

二、实验原理

地址单元主要由三部分组成:程序计数器、地址寄存器和多路开关。

程序计数器PC用以指出下一条指令在主存中的存放地址,CPU正是根据PC的内容去存取指令的。因程序中指令是顺序执行的,所以PC有自增功能。程序计数器提供下一条程序指令的地址,在T4时钟脉冲的作用下具有自动加1的功能;在LDPC信号的作用下可以预置计数器的初值(如子程序调用或中断响应等)。当LDPC为高电平时,计数器装入data[ ]端输入的数据。aclr是计数器的清0端,高电平有效(高电平清零);aclr为低电平时,允许计数器正常计数。

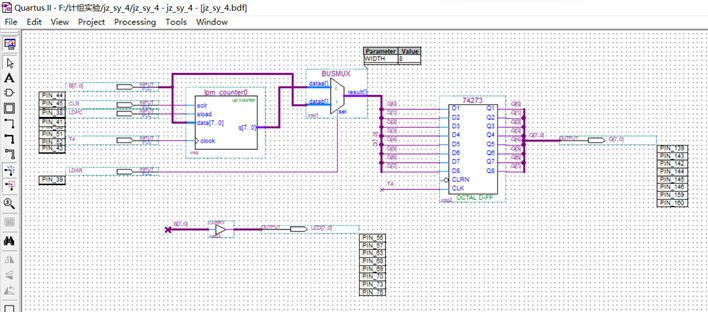

三、实验电路图

该部分由程序计数器、地址寄存器和多路开关组成,输入端CLR为异步清零,输入端SLOAD为同步置数端,置的数值根据输入的8位地址线确定。T4输入端接入时钟信号。多路开关BUSMUX控制信号的选择,SEL为控制信号,当SEL为0时选择的信号为输入的地址,当SEL为1时选择的信号为计数器中输出的数据。后输入到74273地址寄存器中。

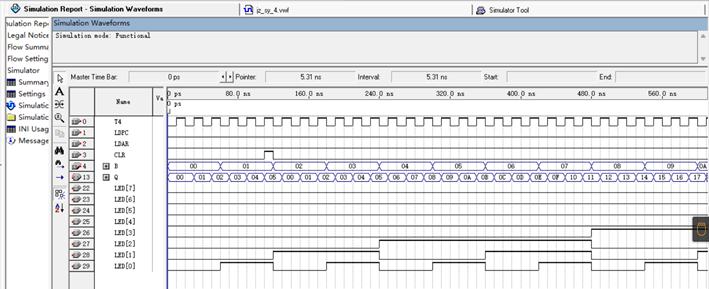

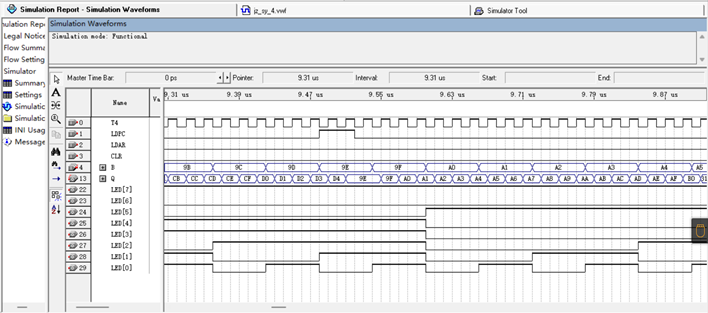

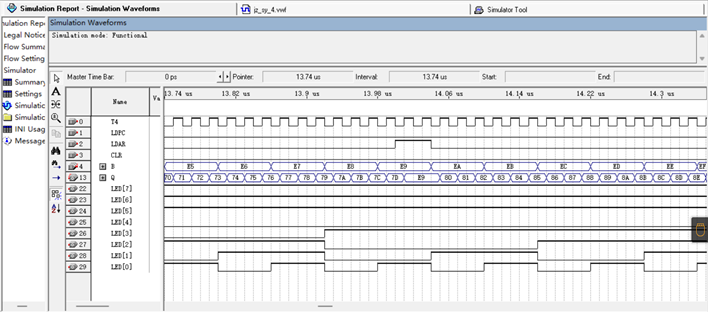

四、实验波形图

由该波形图可以看出,当CLR输出为高电平时,在下一个上升沿到来时,计数器清零,重新从00开始计数。

由该波形图可以看出,当LDPC输入为高电平时,计数器的置数端有效,根据所给出的地址将计数器值置为该地址的数据,并输出出来。

由该波形图可以看出,当LDAR输入为高电平时,BUSMUX直接选择地址的数据,从而输出为地址。但并不会对计数器内的状态产生影响,当LDAR回到低电平时,继续输出计数器内的数值。

五、实验心得

掌握了程序计数器PC和地址寄存器AR的工作原理,并在功能仿真软件中模拟验证了模块的功能。

实验五 总线控制实验

一、实验目的

1.理解总线的概念及特性。

2.掌握总线传输控制特性。

二、实验原理

总线是多个系统部件之间进行数据传输的公共通路,是构成计算机系统的骨架。借助总线连接,计算机在系统各部件之间实现传送地址、数据和控制信息的操作。所谓总线就是指能为多个功能部件服务的一组公用信息线。

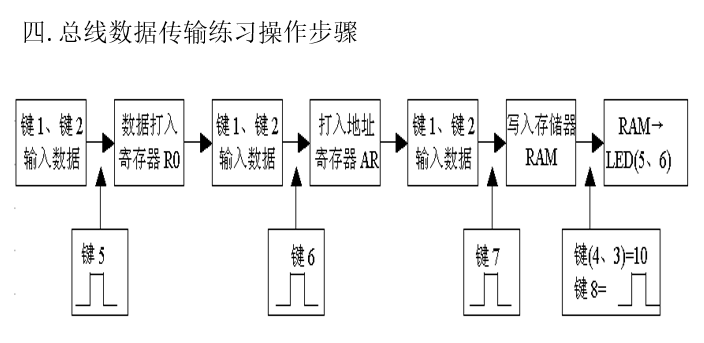

三.实验内容

根据挂在总线上的几个基本部件,设计一个简单的流程。

1.输入设备将数据打入寄存器R0。

2.输入设备将另一个数据打入地址寄存器AR。

3.将寄存器R0中的数据写到当前地址的存储器中。

4.将当前地址的存储器中的数用数码管显示。

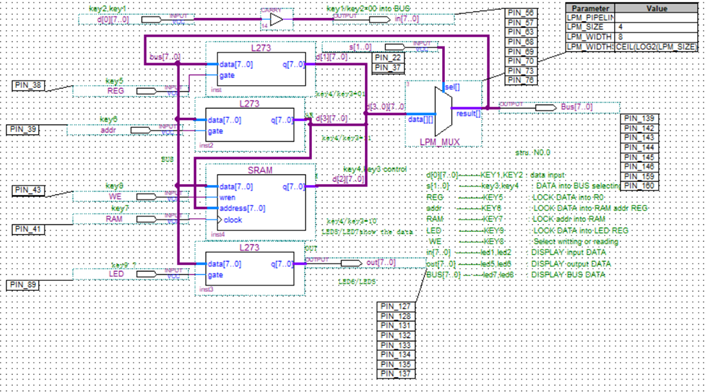

四、实验电路图

该电路的电路图如下所示

键1和键2控制输入的数据,显示在1和2数码显示管上。键3和键4控制当前显示的寄存器数据,00为当前键1、2控制的数据,01为R0寄存器,11为AR寄存器,10为RAM存储器的数据。而键5控制R0寄存器的使能端,键6控制AR寄存器的使能端,键7控制RAM存储器的使能端,注意在用键7写入数据前,需要将键8置为高电平状态。键8控制读写允许,当为高电平时允许写入。

五、实验心得

掌握了总线传输数据的步骤,理解了CPU操作处理的汇编操作。